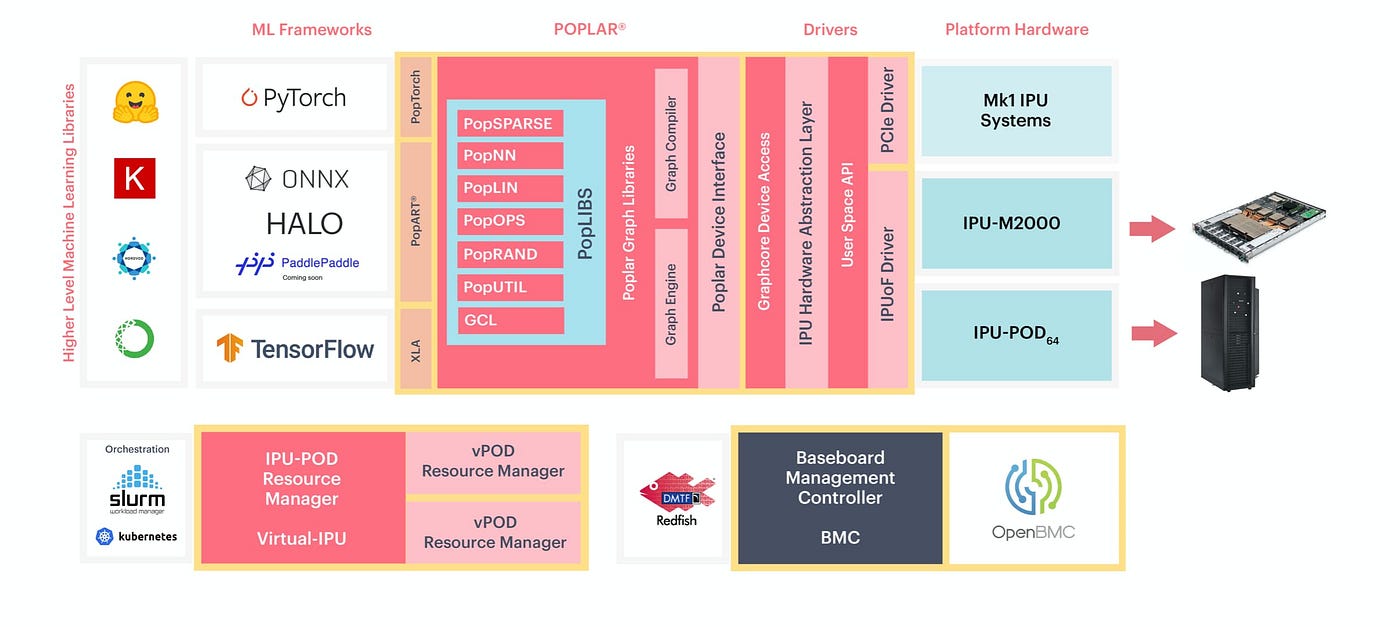

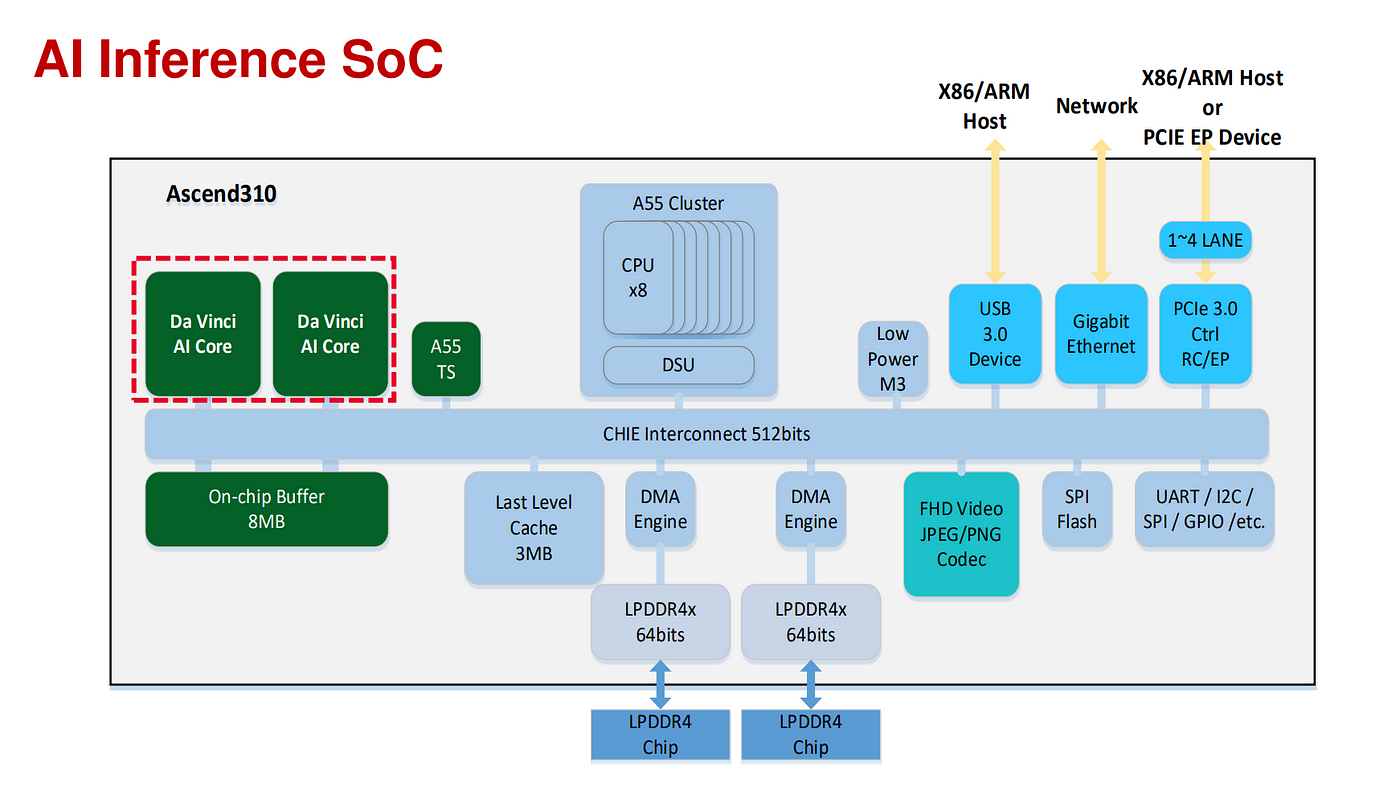

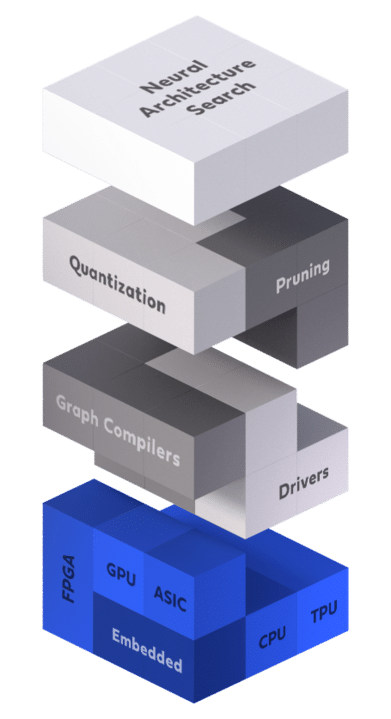

Arch-Net: A Family Of Neural Networks Built With Operators To Bridge The Gap Between Computer Architecture of ASIC Chips And Neural Network Model Architectures - MarkTechPost

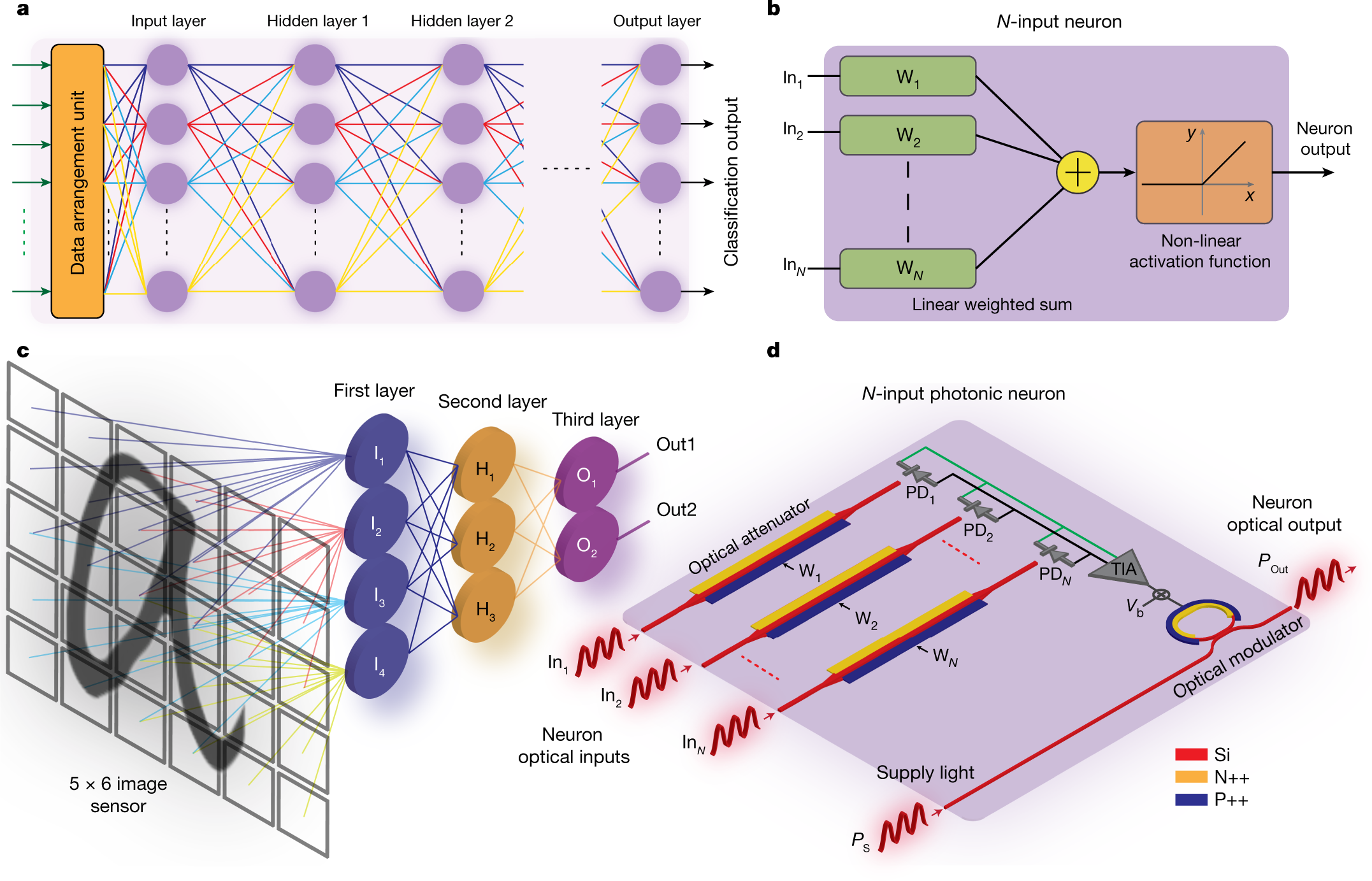

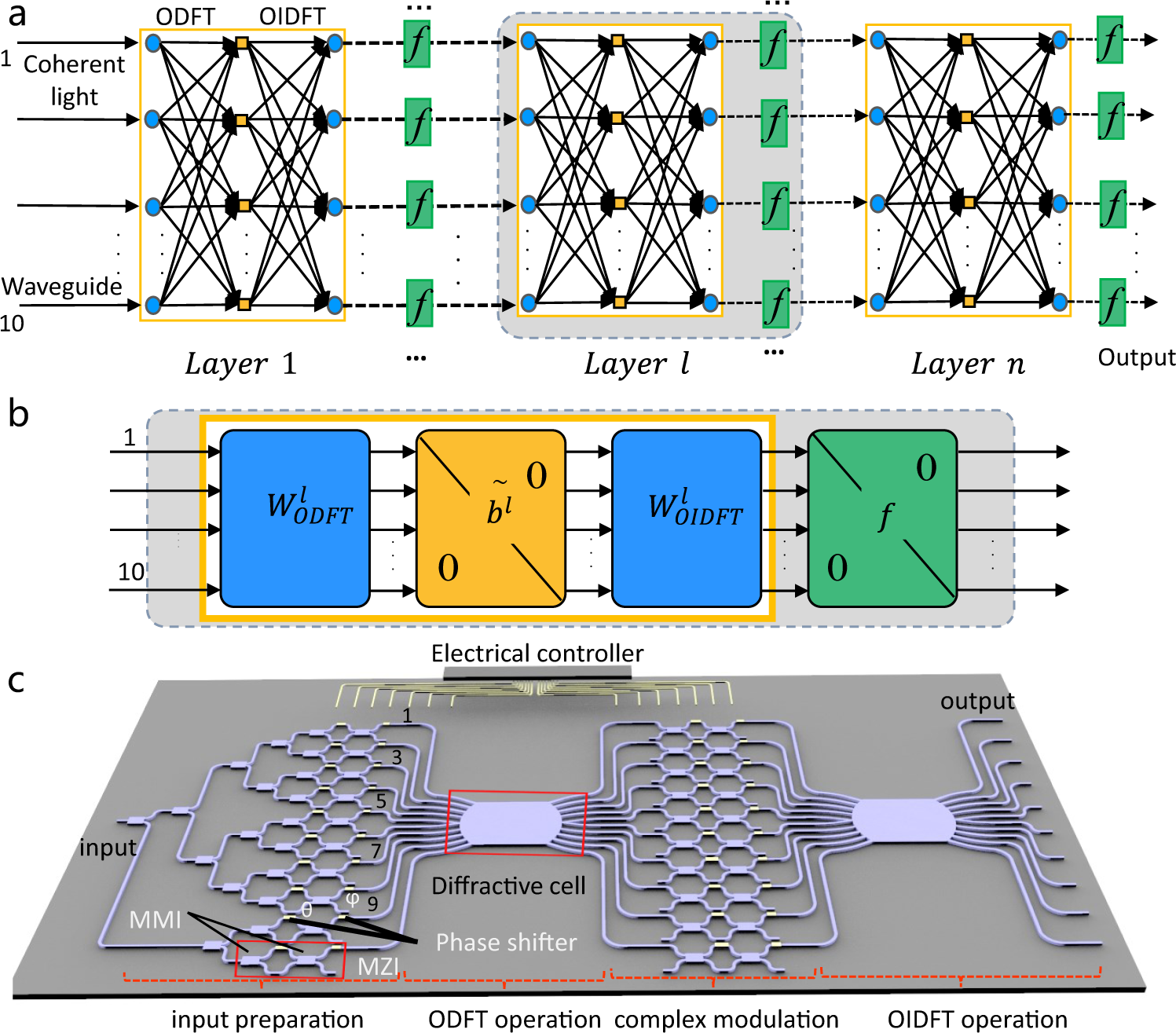

Space-efficient optical computing with an integrated chip diffractive neural network | Nature Communications